# CPE 470 - CocoTB

## **Verification Challenges**

- Verification is inherently software

- Runs only in simulator

- Verilog / System Verilog originally designed as HDL

- Specialized for describing hardware, not software

- System Verilog does have OOP features

- Steep learning curve

- Less modernized

#### System Verilog Class

```

class myPacket;

bit [2:0]

header;

bit

encode:

bit [2:0] mode;

bit [7:0] data;

bit

stop;

function new (bit [2:0] header = 3'h1, bit [2:0] mode = 5);

this.header = header;

this encode = 0:

this.mode = mode:

this.stop = 1;

endfunction

function display ();

$display ("Header = 0x%0h, Encode = %0b, Mode = 0x%0h, Stop = %0b",

this.header, this.encode, this.mode, this.stop);

endfunction

endclass

```

#### YOU'RE TELLING ME

A PYTHON TESTED THIS BENCH

#### **Glossary**

#### Coco TB

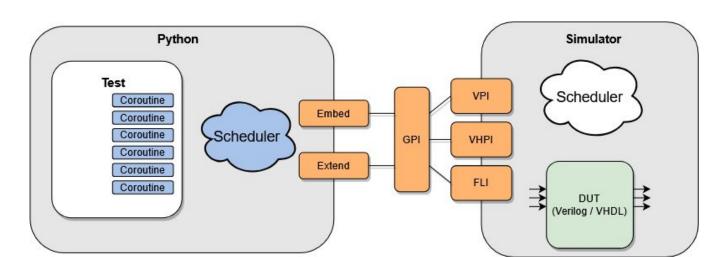

**CocoTB:** Coroutine Co-Simulation Test Bench

**DUT:** device under test, the top-level thing being tested

- **CocoTB** introduces Python-based testbench development

- It is NOT a simulator! It interacts with a simulator

- Uses verilator, icarus, or industry-grade simulator under the hood

- Takes turns between python and simulator

- Python Code Introduces New Data to DUT

- Waits while simulator executes a time step

- Back and forth between python and simulator of choice

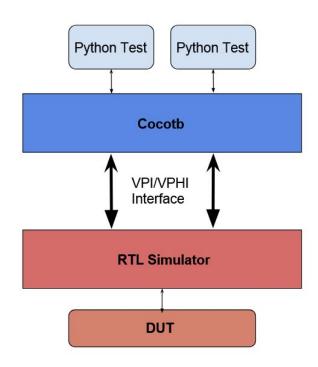

#### **CocoTB Structure**

- Use CocoTB in addition to (or instead of) verilog test bench

- Often useful to have both kinds

- Write multiple python tests

- Every time tests hit a delay or clock event, will defer to simulator

- After event, simulator sends results back to python

- Abstract common operations into python classes

- Create more easily reusable blocks to drive inputs and monitor outputs

### **Setting Up a Test**

- Each test configured with a Makefile

- Abstracts away the build process for different simulators

- Easy to switch between them

- Somewhat Language Agnostic

- Could bring same testbench to VDHL

- Only switch lang and simulator

- Can turn waves on and off

- Often don't want waves for sufficiently large tests

```

TOPLEVEL LANG ?= verilog

SIM ?= icarus

VERILOG SOURCES = top.sv # List of Source Files

# Folders to look for source files

VERILOG INCLUDE DIRS = rtl

COCOTB TOPLEVEL

:= top # CocoTB Version 2

TOPLEVEL := $(COCOTB TOPLEVEL)

# CocoTB Version 1

COCOTB_TEST_MODULES := top_test # CocoTB Version 2

MODULE := $(COCOTB TEST MODULES)

# CocoTB Version 1

WAVES := 1 # Turn on waveforms

# Call CocoTB's makefile

include $(shell cocotb-config --makefiles)/Makefile.sim

```

## **Interacting With DUT**

```

Writing a Signal:

```

- Reading a Signal:

- Reading a Nested Signal:

- CocoTB always uses non-blocking assignment (<=)</li>

- Values will not get updated in your **DUT** until a timestep occurs

- Reading a value reads the value from the last time step, not updated value

```

x = dut.signal.value

y = dut.module.signal.value

dut.signal.value = 0

await RisingEdge(dut.clk_w) # Timestep

dut.signal.value = 1

```

dut.signal.value = 1

x = dut.signal.value

# x will be 0

## **Simulation Time Steps**

Simulation only happens during a timestep. Each main SV time step has a CoCoTB analogue.

|                     | System Verilog                                        | СосоТВ                                                                   |

|---------------------|-------------------------------------------------------|--------------------------------------------------------------------------|

| Delay               | #(1)                                                  | <pre>await Timer(1, units="ns")</pre>                                    |

| Creating<br>a Clock | <pre>always begin   #(20)   clk &lt;= ~clk; end</pre> | <pre>clock = Clock(dut.clk_i, 10) cocotb.start_soon(clock.start())</pre> |

| Clock Edge          | <pre>@(posedge clk); @(negedge clk);</pre>            | <pre>await RisingEdge(dut.clk) await FallingEdge(dut.clk)</pre>          |

| Assertions          | assert (clk == 0);                                    | assert clk == 0                                                          |

There is no version of system verilog's wait, other than a while loop with delays / edges.

### **CocoTB Concurrency**

- CocoTB uses Python's asyncio library to handle concurrency

- Declare functions as async to use them as coroutines

- Each can interact with DUT

- Each can fail

Use await to suspend a coroutine as it waits for another one

Equivalent to having multiple always blocks in system verilog

```

async def function1 (dut):

pass

async def function2 (dut):

pass

@cocotb.test()

async def main_test(dut):

task1 = cocotb.start soon(function1(dut))

task2 = cocotb.start_soon(function2(dut))

await task1

await task2

```

### **CocoTB Tradeoffs**

- + CocoTB enables use of a higher level language

- Great for file IO, simulating external devices (VGA, Memories, etc.)

- + Libraries for common interfaces (AXI, Wishbone, etc.)

- Slower than raw SV simulation

- Python is slow enough, moving back and forth between Python and Simulator is extra slow

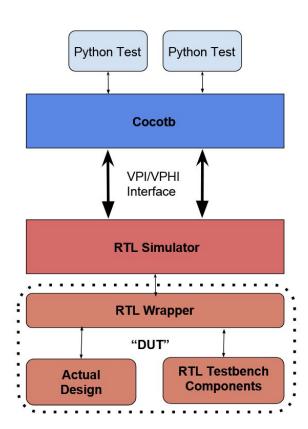

- Can't do top level integration

- In SV, can instantiate more than one module in testbench and hook them up

- Can't instantiate more than one module in cocotb

- If more modules are needed, have to create a verilog wrapper top level module

#### **CocoTB Bus Extension**

- Fix Outdated CocoTB Fork, Case Sensitivity (#1)

- fk

# Attach Wishbone Master to Bus

fkwilken authored on Dec 10, 2023

- CocoTB allows powerful abstraction of buses

- Wishbone, AXI, etc.

- Verify your design against open source standards

- Can encapsulate signals in an object

- Wishbone Example uses a dictionary to define signal names

- Abstracted reads and writes

```

wbs = WishboneMaster(dut, "wbs", dut.wb clk i,

width=32, # size of data bus

timeout=10, # in clock cycle number

signals_dict={"cyc": "cyc_i",

"stb": "stb i",

"we": "we_i",

"adr": "adr i",

"datwr": "dat i",

"datrd": "dat o",

"ack": "ack o",

"sel": "sel i" })

# Create Write Operation

wb op = WBOp(adr, dat, 0, sel=0xF)

wbs.send cycle([wb op])

# Create Read Operation

wb op = WBOp(adr,None,0,sel=0xF)

read resp = wbs.send cycle([wb op])

```

### **CocoTB Example**

https://github.com/cocotb/cocotb/blob/master/examples/adder/tests/test\_adder.py

https://github.com/cocotb/cocotb/blob/master/examples/simple\_dff/test\_dff.py

### References

- https://docs.cocotb.org/en/stable/

- https://indico.cern.ch/event/776422/attachments/1769690/2874927/coco tb\_talk.pdf

- <a href="https://www.chipverify.com/systemverilog/systemverilog-class">https://www.chipverify.com/systemverilog/systemverilog-class</a>